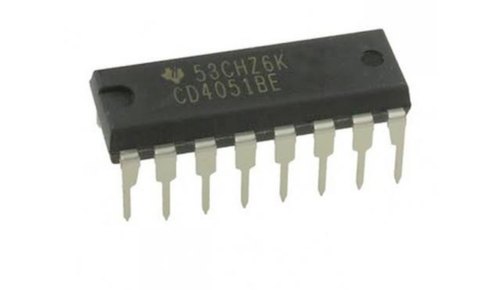

Dual 4-Stage Static Shift Register (CD4015BE)

0.200ر.ع.

5 in stock

SKU: ICM-00043

Categories: ICs, Integrated Circuits (ICs) & Modules

CD4015BE consists of two identical, independent, 4-stage serial-input/parallel-output registers. Each register has independent CLOCK and RESET inputs as well as a single serial DATA input. “Q” outputs are available from each of the four stages on both registers. All register stages are D-type, master-slave flip-flops.

- Medium speed operation…12 MHz (typ.) clock rate at VDD – VSS = 10 V

- Fully static operation

- 8 master-slave flip-flops plus input and output buffering

- 100% tested for quiescent current at 20 V

- 5-V, 10-V, and 15-V parametric ratings

- Standardized, symmetrical output characteristics

- Maximum input current of 1 µA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package-temperature range) =

- 1 V at VDD = 5 V

- 2 V at VDD = 10 V

- 2.5 V at VDD = 15 V

- Meets all requirements of JEDEC Tentative Standard No. 13B, “Standard Specifications for Description of ’B’ Series CMOS Devices”

- Applications:

- Serial-input/parallel-output data queueing

- Serial to parallel data conversion

- General-purpose register

Be the first to review “Dual 4-Stage Static Shift Register (CD4015BE)” Cancel reply

You must be logged in to post a review.

Reviews

There are no reviews yet.